- Blog

- New Page

- Ratsasan Tamil Movie Online

- Brie Larson Wei?e Manner

- Rsd Lite 6.0

- Bescor Over Ehernet

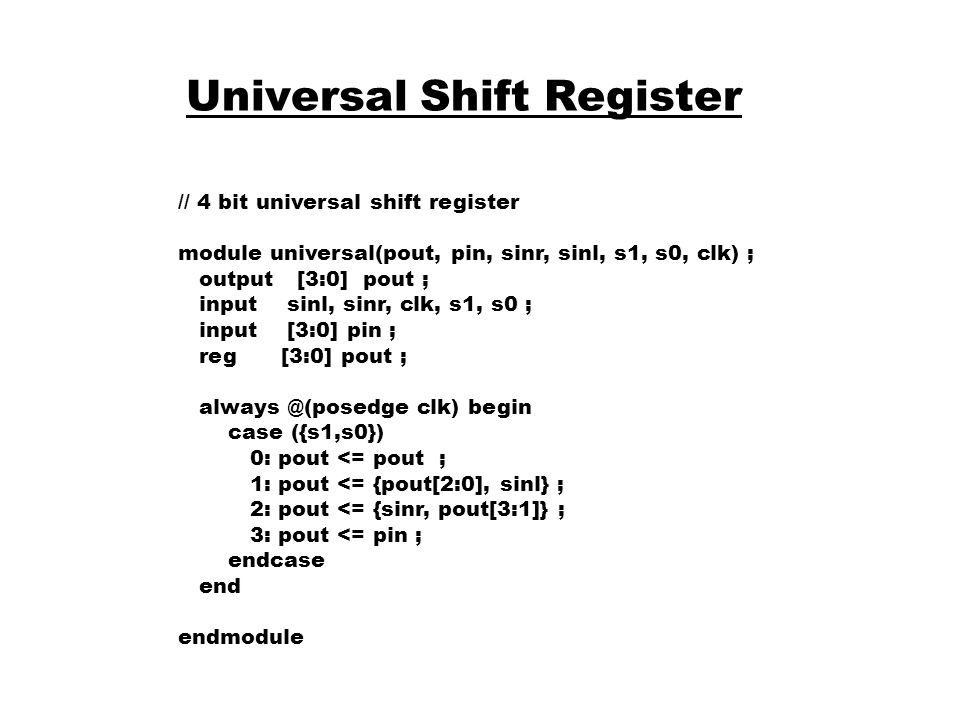

- Behavioral Verilog Code For A 4-bit Binary Shift Register

- Exception Plan Request

- Mariela Graham Principal Brooklyn

- Steve Weiss Music

- Ex4 Mql4 Decompiler 1090

- Halo 2 Maps

- Lke2600 Driver Download

- Ptk Bahasa Indonesia

- Ez Check Printing License Key

- Games For 4gb Ram And 1gb Graphic Card

- M3 Carbine Manual

- Greco Fa67 175 Neck Specs

- Java How To Turn Keycode Into Letters

- Proposal Ptk Tematik Kelas 4

- Sam smith in the lonely hour www-jambaze-com

- How to add celebrity voices on waze

- How to set up messages on a mac

- Macbook software update date

- Bs player pro apk download

- Wacom bamboo ink stylus compatibility

- How to clean up mac memory

- How to make a bootable usb mac os x mojave

- Zombie and medieval games steam

- Free online virus scan google chrome

- Mahabharat serial songs free download

- How to find data analysis in microsoft excel 2011 for mac

Design of Parallel In - Serial OUT Shift Register using Behavior Modeling Style - Output Waveform: Parallel IN - Serial OUT Shi. 4 to 1 Multiplexer Design using Logical Expression (Verilog CODE) 4 to 1 Multiplexer Design using Logical Expression (Data Flow Modeling Style)- Output Waveform: 4 to 1 Multiplexer Program.

1. The problem statement, all variables and given/known data

My homework is to design a Serial Adder in Verilog using a shift register module, a full adder module, and a D Flip-Flop module.

I know my full adder and flip flop modules are correct, but I am not so sure about my shift register. The shift register is 8 bits:

Inputs for the shift register are: Si, CLK, Reset

Outputs for the shift register are: So, D7 through D0 (one for each bit of the register)

Also, if anyone can give me a hint as to how I can approach designing a test bench would be extremely helpful.

3. The attempt at a solution

My homework is to design a Serial Adder in Verilog using a shift register module, a full adder module, and a D Flip-Flop module.

I know my full adder and flip flop modules are correct, but I am not so sure about my shift register. The shift register is 8 bits:

Inputs for the shift register are: Si, CLK, Reset

Outputs for the shift register are: So, D7 through D0 (one for each bit of the register)

Also, if anyone can give me a hint as to how I can approach designing a test bench would be extremely helpful.

3. The attempt at a solution